Giriş:

Çalt depginde ösýän tehnologiki döwürde çalt prototip ýazmagyň zerurlygy, esasanam çap edilen tagtanyň (PCB) ösüş pudagynda ägirt uly güýje eýe boldy. Engineöne in engineenerler tizligiň PCB-iň signal bitewiligine täsir etmezligini nädip üpjün edip bilerler?Bu blogda, signalyň bitewiligini göz öňünde tutup, çalt PCB prototip ýazmak sungatyny özleşdirmäge kömek etjek strategiýalary we iň oňat tejribeleri öwreneris.

PCB dizaýnynda signalyň bitewiliginiň ähmiýetine düşüniň:

Signalyň bitewiligi, signalyň geçiriş wagtynda ýoýulmazdan, peselmezden ýa-da ýitirilmezden PCB arkaly ýaýramak ukybyna degişlidir. Signal bütewiliginiň pes bolmagy maglumatlaryň ýalňyşlyklary, öndürijiligiň peselmegi we päsgelçiliklere duýgurlygynyň ýokarlanmagy ýaly dürli problemalara sebäp bolup biler. PCB-leri prototip edende, soňky önümiň işleýşini we ygtybarlylygyny üpjün etmek üçin signalyň bitewiligini ileri tutmak möhümdir.

1. Signalyň bitewiligini dizaýn görkezmelerine eýeriň:

Signalyň optimal bitewiligini üpjün etmek üçin prototip ýazmak döwründe ýörite dizaýn görkezmeleri berjaý edilmelidir. Bu görkezmeler şulary öz içine alýar:

A. Komponentleri dogry ýerleşdirmek: Komponentlere strategiki taýdan ýerleşdirmek, signal yzlarynyň uzynlygyny azaltmaga kömek edýär we şeýlelik bilen signalyň zaýalanmak howpuny azaldýar.Baglanyşykly komponentleri bir ýere jemlemek we öndürijiniň ýerleşdiriş tekliplerine eýermek, signalyň bitewiligini optimizirlemekde möhüm ädimlerdir.

b. Yzyň uzynlygynyň gabat gelmegi: speedokary tizlikli signallar üçin yzygiderli yz uzynlygyny saklamak, wagtyň gyşarmagynyň we signalyň ýoýulmagynyň öňüni almak üçin möhümdir.Potensial wagt gabat gelmezliklerini azaltmak üçin şol bir signallary göterýän yzlaryň birmeňzeş uzynlygyna göz ýetiriň.

C. Impedans gözegçiligi: Geçiriji liniýanyň häsiýetli päsgelçiligine gabat gelýän PCB yzlaryny taslamak, şöhlelenmeleri azaltmak arkaly signalyň bitewiligini ýokarlandyrýar.Impedans dolandyryş usullary, gözegçilik edilýän impedans marşruty ýaly ýokary ýygylykly programmalarda möhüm ähmiýete eýe.

2. Öňdebaryjy PCB dizaýn gurallaryny ulanyň:

Signalyň bitewiligini seljermek mümkinçilikleri bilen enjamlaşdyrylan iň täze PCB dizaýn programma üpjünçiligini ulanmak prototip ýazmak işini ep-esli aňsatlaşdyryp biler. Bu gurallar in engineenerlere signalyň bitewiligini ýüze çykarmak mümkinçiligini ir kesgitlemek üçin önümçilikden öň PCB dizaýnlarynyň özüni alyp barşyny simulirlemäge we seljermäge mümkinçilik berýär.

A. Simulýasiýa we modellemek: Simulýasiýalary ýerine ýetirmek, signalyň özüni alyp barşyna giňişleýin baha bermegi, signalyň bitewiligi bilen baglanyşykly meselelere düşünmegi üpjün edýär.Dürli ssenariýalary simulirlemek bilen dizaýnerler şöhlelenme, pyýada ýörelgesi we elektromagnit päsgelçiligi (EMI) bilen baglanyşykly meseleleri kesgitläp we düzedip bilerler.

b. Dizaýn düzgünini barlamak (DRC): PCB dizaýn programma üpjünçiliginde DRC-ni durmuşa geçirmek, dizaýnyň belli bir signal bitewiliginiň görkezmelerine laýyk gelmegini üpjün edýär.Potensial dizaýn kemçiliklerini wagtynda tapmaga we çözmäge kömek edýär.

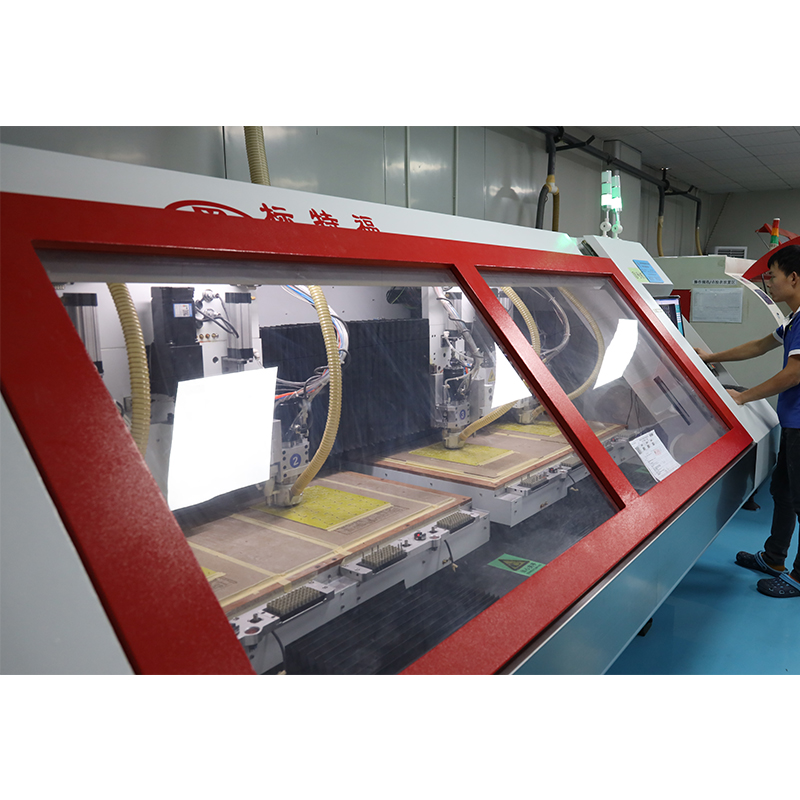

3. PCB öndürijileri bilen hyzmatdaşlyk:

Tejribeli PCB öndürijisi bilen ýakyndan işlemek prototip ýazmak işini ep-esli aňsatlaşdyryp biler. Öndürijiler signalyň bitewiligi meselesi barada gymmatly düşünje berip bilerler we dizaýny optimizirlemek üçin üýtgetmeleri maslahat berip bilerler.

A. Materiallary saýlamak: Öndüriji bilen işlemek, PCB dizaýnyňyz üçin dogry materiallary saýlamaga mümkinçilik berer.Pes dielektrik ýitgi tangenti we gözegçilik edilýän dielektrik hemişelik materiallar signalyň bitewiligini ýokarlandyryp biler.

b. Önümçilik üçin dizaýn (DFM): Dizaýn döwründe öndürijileri çekmek dizaýnyň önümçilik üçin optimallaşdyrylmagyny üpjün edýär we pes öndürijilik sebäpli ýüze çykýan signal bitewiligini peseldýär.

4. Iterative synag we optimizasiýa:

Prototip gutaransoň, signalyň bitewiligini barlamak üçin düýpli synaglar geçirilmelidir. Synagyň gaýtalanýan prosesi, meseleleri kesgitlemek we optimizasiýalary amala aşyrmak ajaýyp signal bitewiligini gazanmak üçin möhümdir.

Sözümiň ahyrynda:

Signal bitewiligini göz öňünde tutup çalt PCB prototip bermek kyn bolup biler, ýöne dogry dizaýn usullaryny ulanmak, öňdebaryjy PCB dizaýn gurallaryny ulanmak, öndürijiler bilen hyzmatdaşlyk etmek we iteratiw synag geçirmek arkaly in engineenerler bazara çalt wagt gazanyp, signalyň bitewiligini optimizirläp bilerler.Prototip ýazmak prosesinde signalyň bitewiligini ileri tutmak, soňky önümiň ygtybarly işlemegini we häzirki zaman elektronika pudagynyň talaplaryny kanagatlandyrmagyny üpjün edýär.

Iş wagty: Oktýabr-21-2023

Yzyna